硬件設(shè)計(jì)語言發(fā)展

VHDL語言從70年代末和80年代初開始發(fā)展,起源于美國(guó)國(guó)防部VHSIC計(jì)劃,該計(jì)劃的目標(biāo)是開發(fā)下一代高集成度的IC芯片,使用的是門級(jí)工具。但對(duì)于10萬門級(jí)的設(shè)計(jì)使用門級(jí)工具顯然會(huì)力不從心,于是在80年代初,硬件描述語言VHDL被提出來,用于描述復(fù)雜的邏輯電路和作為標(biāo)準(zhǔn)的交換文件,此后,VHDL被不斷發(fā)展和完善,參加和支持的廠商越來越多,直到1987年VHDL被正式接納為IEEE1076- 87標(biāo)準(zhǔn)從此,電子邏輯設(shè)計(jì)開始擺脫設(shè)計(jì)人員帶有濃重個(gè)人風(fēng)格的設(shè)訓(xùn)思路,而采用標(biāo)準(zhǔn)化模塊和確定的語言描述來加以規(guī)范。到1993年,IEEE1076- 87被改版為93年版,進(jìn)一步完善了標(biāo)準(zhǔn)化的模塊,增強(qiáng)了模塊的功能。 2100433B

硬件設(shè)計(jì)語言造價(jià)信息

計(jì)算機(jī)輔助工程軟件的供應(yīng)商已把VHDL作為其CAD或EDA軟件輸入與輸出的標(biāo)準(zhǔn),例如SYNOPSYS ALTERA CA-DENCE VIEW LOGIC等EDA廠商均提供了VHDL的編譯器,并在其仿真工具、綜合工具和布圖工具中提供了對(duì)VHDL的支持。特別值得一提的是ALTERA公司不僅提供大規(guī)模的CPLD和FPGA器件,同時(shí)也提供一套十分有特色的綜合工具M(jìn)AXPLUS- II,設(shè)計(jì)者既可以使用原理圖輸入,也可以使用文本輸入方式,更可以二者混合輸入。

硬件設(shè)計(jì)語言發(fā)展常見問題

-

典型的人工智能語言主要有LISP、Prolog、Smalltalk、C++等。在人工智能手冊(cè)中介紹了七種人工智能語言:LISP,PLANNER,CINNIVER,QLISP,POP-2,SAIL,FU...

-

一、幼兒園的規(guī)模(包括托、幼合建的)分為:大型:10個(gè)班至12個(gè)班。中型:6個(gè)班至9個(gè)班。小型:5個(gè)班以下。二、單獨(dú)的托兒所的規(guī)模以不超過5個(gè)班為宜。三、托兒所、幼兒園每班人數(shù):1.托兒所:乳兒班及托...

-

Java語言發(fā)展趨勢(shì)一直處于持平,排名前三,可見企業(yè)用Java的人還是很多,雖然今年遇到互聯(lián)網(wǎng)寒冬,對(duì)于Java程序員來說,可能競(jìng)爭(zhēng)更激烈,Java程序員的招聘比起以前更嚴(yán)格,所以,還是努力學(xué)習(xí)Jav...

硬件設(shè)計(jì)語言發(fā)展文獻(xiàn)

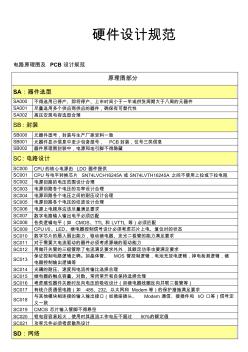

硬件設(shè)計(jì)規(guī)范

硬件設(shè)計(jì)規(guī)范

格式:pdf

大小:90KB

頁數(shù): 7頁

評(píng)分: 4.8

電路原理圖及 PCB 設(shè)計(jì)規(guī)范 原理圖部分 SA:器件選型 SA000 不得選用已停產(chǎn)、即將停產(chǎn)、上市時(shí)間小于一年或供貨周期大于八周的元器件 SA001 盡量選用多個(gè)供應(yīng)商供應(yīng)的器件,確保有可替代性 SA002 高壓安規(guī)電容選型合理 SB:封裝 SB000 元器件型號(hào),封裝與生產(chǎn)廠家資料一致 SB001 元器件顯示信息中至少包含型號(hào), PCB封裝,位號(hào)三類信息 SB002 器件原理圖封裝中,電源和地引腳不得隱藏 SC:電路設(shè)計(jì) SC000 CPU的核心電源由 LDO 器件提供 SC001 CPU與電平轉(zhuǎn)換芯片 SN74LVCH16245A 或 SN74LVTH16245A 之間不使用上拉或下拉電阻 SC002 電源回路的電壓范圍設(shè)計(jì)合理 SC003 電源回路各個(gè)電壓的功率設(shè)計(jì)合理 SC004 電源回路各個(gè)電壓之間的耐壓設(shè)計(jì)合理 SC005 電源回路各個(gè)電壓的紋波設(shè)計(jì)合理 SC006 電源上

- 相關(guān)百科

- 相關(guān)知識(shí)

- 相關(guān)專欄

- 硬件設(shè)計(jì)驗(yàn)證

- 硬件

- 硬化系數(shù)

- 硬葉蘭

- 硬葉蘭海南個(gè)體

- 硬葉蘭(亞種)

- 硬葉常綠闊葉林

- 硬葉組

- 硬度指標(biāo)

- 硬度表

- 硬盤主引導(dǎo)記錄修復(fù)

- 硬盤分區(qū)格式轉(zhuǎn)換

- 硬盤實(shí)戰(zhàn)維修從入門到精通

- 硬盤式攝像機(jī)

- 硬盤攝像機(jī)

- 硬盤數(shù)據(jù)恢復(fù)軟件

- 中國(guó)被動(dòng)式太陽房及太陽能建筑市場(chǎng)監(jiān)測(cè)及發(fā)展策略研

- 中國(guó)工程造價(jià)咨詢業(yè)的發(fā)展趨勢(shì)

- 中國(guó)民宿消費(fèi)市場(chǎng)格局分析及十三五發(fā)展環(huán)境分析報(bào)告

- 在創(chuàng)新中求發(fā)展——樂山市土地儲(chǔ)備中心工作創(chuàng)新紀(jì)實(shí)

- 中國(guó)房地產(chǎn)投資信托基金(REITs)發(fā)展模式探索

- 在加快天津城市綠化建設(shè)中不斷創(chuàng)新發(fā)展的園林局工會(huì)

- 中國(guó)讀卡器市場(chǎng)現(xiàn)狀分析及未來五年發(fā)展前景分析報(bào)告

- 中國(guó)水泥溝蓋板市場(chǎng)發(fā)展及投資前景報(bào)告

- 以浙江省公路養(yǎng)護(hù)機(jī)械化的發(fā)展看筑養(yǎng)路機(jī)械市場(chǎng)需求

- 一心一意謀發(fā)展 中國(guó)重型汽車集團(tuán)有限公司發(fā)展紀(jì)實(shí)

- 制水泥樓板市場(chǎng)現(xiàn)狀調(diào)研及發(fā)展前景分析報(bào)告(目錄)

- 中國(guó)水利水電第十六工程局有限公司機(jī)場(chǎng)施工發(fā)展戰(zhàn)略

- 中國(guó)國(guó)際太陽能光伏建筑一體化技術(shù)發(fā)展

- 以思想解放推進(jìn)發(fā)展新跨越竭力打造中原建設(shè)工程鐵軍

- 中國(guó)預(yù)應(yīng)力混凝土管樁的發(fā)展?fàn)顩r及同日本管樁的差距

- 云南省高寒山區(qū)發(fā)展被動(dòng)式太陽能建筑的區(qū)域優(yōu)勢(shì)