格式:pdf

大小:358KB

頁數: 3頁

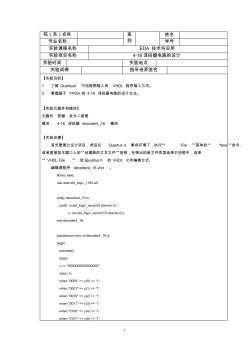

1 院(系)名稱 班 別 姓名 專業名稱 學號 實驗課程名稱 EDA 技術與應用 實驗項目名稱 4-16譯碼器電路的設計 實驗時間 實驗地點 實驗成績 指導老師簽名 【實驗目的】 1. 了解 QuartusII 中電路圖輸入和 VHDL 程序輸入方式。 2. 掌握基于 FPGA 的 4-16 譯碼器電路的設計方法。 【實驗元器件和模塊】 元器件:按鍵、發光二極管 模塊: 4-16 譯碼器 decoder4_16 模塊 【實驗步驟】 首先要建立設計項目,然后在 Quartus II 集成環境下,執行“ File ”菜單的“ New”命令, 或者直接按主窗口上的“創建新的文本文件”按鈕,在彈出的新文件類型選擇對話框中,選擇 “ VHDL File ”,進入Quartus II 的 VHDL 文本編輯方式。 編輯源程序 decoder4_16.vhd 。 library ieee; use

格式:pdf

大小:95KB

頁數: 3頁

【例 4.15】用模塊例化方式設計 8位計數譯碼器電路系統。 在 8 位計數譯碼系統電路設計中, 需要事先設計一個 4 位二進制加法計數器 cnt4e 模塊 和一個七段數碼顯示器的譯碼器 dec7s模塊,然后用模塊例化方式將這兩種模塊組成計數譯 碼系統電路。 1. 4位二進制加法計數器 cnt4e 的設計 cnt4e 的元件符號如圖 4.11 所示, clk 是時鐘輸入端; clr 是復位控制輸入端,當 clr=1 時計數器被復位,輸出 q[3..0]=0000;ena 是使能控制輸入端,當 ena=1 時,計數器才能工 作; cout 是進位輸出端,當輸出 q[3..0]=1111 時, cout=1。 Cnt4e 的 Verilog HDL 源程序 cnt4e.v 如下: module cnt4e (clk,clr,ena,cout,q); input clk,clr,ena; o

熱門知識

38譯碼器-

話題: 工程造價kei19820505

-

話題: 工程造價45dj2679li

精華知識

38譯碼器最新知識

38譯碼器相關問答

38譯碼器-

話題: 工程造價qzkewei18473

- 直徑38公分廣玉蘭報價

- 金剛石瓷磚38元一塊能買嗎

- 華百安可視門鈴x5-fc38v報價

- 管子螺紋Z38是什么意識

- 高鋁耐火磚T38尺寸

- 高壓油管38*1000什么價格

- 常德恒大華府38號棟價格

- 常州補充定額8-B38工作內容

- 寶馬G38前胎多少錢

- t型龍骨38與32的區別

- 壓裂泵閥箱鍛坯用38CrNi2.5MoV鋼的生產試制

- 吉林石化公司38萬t/a乙烯裝置裂解爐改造完成50%

- 國家安監總局令第38號尾礦庫安全監督管理規定

- 38mm×1820mm熱軋超低碳帶鋼熱壓縮變形抗力

- 38—53m厚大體積混凝土樁承臺施工及裂縫控制

- RTKZ-38水內冷發電機絕緣特性測試儀技術規范書

- SYB38瀝青混凝土芯樣密實度試驗記錄表(表干法)

- Sl38碾壓式土石壩和漿砌石壩工程質量等級評定標準

- PT10-SH38進水口北京市市政設計院圖集

- GA38-銀行營業場所安全防范要求

- 800×1200梁需38米支撐木模板與支撐計算書

- 國家安監總局38號令尾礦庫安全監督管理規定

- 川建價發〔2008〕38號定額人工調整

- 38DD350型電解槽陽極鈦板與鋼板的腐蝕原因

- 安徽工業大學38#樓教工住宅工程施工組織設計

- 安監總局令第38號尾礦庫安全監督管理規定

- 工業大學教工住宅工程38棟樓施工組織設計方案